1. Jurnal [Kembali]

Alat dan Bahan pada Percobaan Pratikum Di Laboratorium

1. Panel DL 2203C

2. Panel DL 2203D

3. Panel DL 2203 S

4. Jumper

Alat dan Bahan pada Percobaan Pratikum Di Proteus

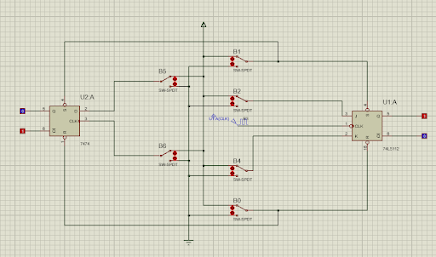

Dari rangkaian terlihat jika switch memberikan input berupa, B0=1, B1=1, B2=0, B3=Clock, B4=1, B5=1, B6=1, terlihat jika B2 yang memberikan '0' terhuung ke pin J dari JK flip-flop, dan B4 yang berlogika '1' terhubung ke K dari JK flip-flop, kondisi pada saatt J='0' dan K='1' disebut kondisi Reset, dimana pada saat kondisi reset, nilai keluaran atau Q di reset ke logika '0', sehingga komplementer keluaran atau Q komplementer berlogika '1', dari rangkaian terbkti jika Q='0' dan Q komplementer='1'. Pada rangkaian D flip-flop, Pin D mendapatkan logika dari B=5 yang berlogika '1' dan clock yang berlogika '1' juga. Tetapi karena D flip-flop belum membaca logika '1' pada clock, sehingga D flip-flop membaca logika '1' dan clock membaca logika '0' karena clock disini membaca detakan awal untuk memulai yang berlogika '0', sehingga pada kondisi ini nilai keluaran atau Q nya akan mengikuti Q kondisi terakhir, dimana Q pada kondisi terakhir berlogika '0' dan Qkomplementernya berlogika '1'. Hal ini menyebabkan lampu LED yang menyala adalah LED6 dan LED8 karena kedua LED ini terhubung ke Qkomplementer dari rangkaian flip-flop. LED6 terhubng ke Qkomlementer JK flip-flop dan LED8 ke Qkomplementer D flip-flop yang kedua Qkomplemeter berlohgika '1'. Sedangkan, LED5 dan LED7 terhubng ke Q dari rangkaian flip-flop dengan LED5 ke Q dari JK flip-flop dan LED7 ke Q dari D flip-flop yang kedua Q nya berlogika '0'.

5. Vidio [Kembali]

- Bagaimana jika B0 dan B1 sama sama diberi logika 0, apa yang terjadi pada rangkaian?

Jawab : Jika B0 dan B1 diberi logika 0, maka R dan S yang merupakan active low akan aktif yang dimana akan mengeluarkan input sebesar 1,1 yang dapat diartikan bahwa kondisi seperti itu adalah terlarang.

- Bagaimana jika B3 diputuskan atau tidak dihubungkan pada rangkaian apa yang terjadi pada rangkaian?

Jawab : B3 terhubung ke clock, sehingga apabila B3 diputuskan tetapi R dan S masih aktif, diputusnya B3 tidak berpengaruh terhadap output, sedangkan apabila R dan S tidak aktif maka output tidak bisa ditentukan karena tidak ada masukan dari clock yang berfungsi sebagai perespon logika apakah terdapat perubahan di output atau tidak

- Jelaskan apa yang dimaksud kondisi toggle,kondisi not change, dan kondisi terlarang pada flip flop!

Jawab :

- Kondisi toggle adalah saat kondisi masukan mengakibatkan logika keluaran yang berkebalikan dari kondisi sebelumnya saat dipicu

- Kondisi not change adalah kondisi saat output tidak mengalami perubahan dari kondisi sebelumnya

- Kondisi terlarang adalah kondisi disaat nilai output Q dan Q komplemennya sama.

Tidak ada komentar:

Posting Komentar